1958年9月12日,杰克·基尔比(Jack S.Kilby,1923-2005)发现了人类历史上*块集成电路,吹响了人类进入“硅时代”的角。1965年,河北半导体研究所在封锁的环境下,依赖自己的气力,研制乐成一种接纳介质隔离的DTL型数字电路,宣告了*块硅基数字集成电路的降生,中国集成电路产业掀开了历史的一页。

图源:中国电子报

近60年来,我国集成电路产业从无到有,锲而不舍,自主创新,研制出一批又一批的芯片,有力支持了我国国民经济和国家平安的生长。尤其是华为海思的麒麟9000芯片,更是中国芯片的登峰之作。然则,在美国禁令下,中国台积电公司不再为华为公司代工芯片,麒麟9000芯片现在已成为绝唱。那么,现在为止,现役的中国*芯片是怎么样的呢?

一、现役中国*芯片

凭证“谁主张,谁举证”的规则,本文作者给出了“现役中国*芯片”的判断规则:

1.原则上应该有外洋对标芯片产物,而不仅仅是要害手艺;

2.每年的全球市场份额不少于100亿美元;

3.国产芯片的性能参数应该靠近、到达或者跨越外洋对标芯片产物水平;

4.在中国大陆设计及制造,已经进入市场,并取得销售额。

最后,能知足上述4个条件的中国芯片,现在只有长江存储的3D NAND闪存芯片X3-9070。

二、NAND闪存芯片的主要市场职位

半导体存储器是是指通过对半导体电路加以电气控制,使其具备数据存储功效的芯片,具有尺度化、强周期等特点,被称为芯片领域的“*宗的单一产物”, 占有了芯片总市场份额的约25%。半导体存储器普遍应用于盘算机、数据中央、网络通讯、消费电子、汽车电子、工业电子等诸多领域。所谓的“有数据就有存储”!随着物联网、大数据、人工智能的快速生长,海量数据对半导体存储器的存储密度和数据可靠性提出了更高要求。尤其是,固态硬盘消耗了大量的NAND 闪存芯片。

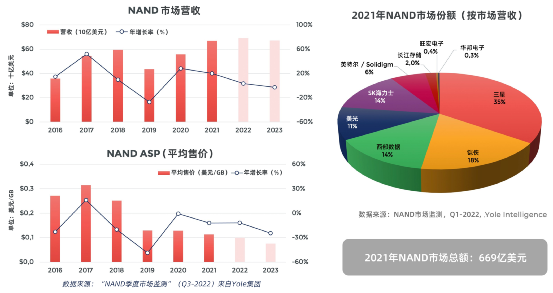

半导体存储器主要包罗DRAM芯片、NAND 闪存芯片和NOR 闪存芯片三个相对自力、各司其职的种别。DRAM 和 NAND FLASH 占有*的主导职位。共计占有半导体存储器市场份额的约98%。在数以万计的芯片种类中,DRAM芯片是当之无愧的“芯片状元”。NAND闪存芯片的市场份额仅略低于DRAM芯片,是当之无愧的“芯片榜眼”!据欧洲着名半导体剖析机构Yole公布的讲述显示,2021年,NAND闪存市场份额到达了近670亿美元,同年,NAND闪存总容量也到达了5855亿GB。

NAND闪存芯片的市场份额 。图源:Yole

三、什么是 平面 NAND闪存芯片?

1984年,日本东芝公司工程师藤尾增冈发现了一种电存储介质。它能在没有电源的情形下存储信息,可以将数据保留达10年以上,这就是闪存的观点。1987年,日本东芝公司研制出了全球*块NAND闪存芯片。其事情原理是一种电压元件,基于电子隧穿效应,将电子注入储存单元中的浮动栅极,从而改变其电荷量,实现信息存储和读取。

2017年4月东芝存储器团体从东芝公司剥离,并于2019年10月正式更名为KIOXIA,中文名为铠侠。当前,铠侠是仅次于韩国三星电子公司的NAND闪存芯片生产厂商。

NAND闪存芯片是一种非易失性手艺,以字节为单元举行编程,以“块(block)” 为单元举行擦除,断电后可耐久保持信息,操作不需要高电压操作,每比特的成本更低,性能更高,成为高密度数据存储的理想载体,普遍应用于移动通讯、消费数码、盘算机、服务器及数据中央。

详细来说,NAND闪存可以电擦除和重新编程。在NAND中,数据存储在存储单元中,并由“0”或“1”示意。一个单元可以存储每个单元1个比特(0,1)以及每个单元2、3和4个比特。在所有情形下,纵然在系统中关闭电源后,数据仍会被存储。

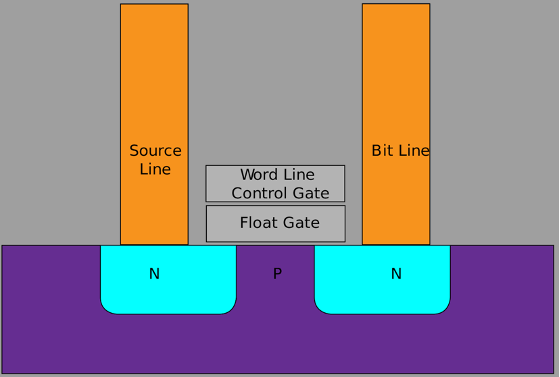

多年来,该行业一直使用平面NAND手艺。在平面NAND中,一系列存储器单元沿着水平串串联毗邻。传统的闪存单元包罗具有控制栅极和浮置栅极的平面晶体管结构。通过向单元施加电压来存储电子并从浮置栅极移除电子。

平面NAND手艺原理。图源:Bing

30多年来,通过改善工艺手艺、电路设计、编程算法和光刻手艺,各大厂商将平面NAND中的单元尺寸从120nm扩展到1xnm节点,使容量增添了100倍。然而,当存储单元结构特征尺寸到达了15nm的极限,平面NAND闪存芯片走到了终点。详细显示为:沟道的掺杂浓度难以控制,随机电报噪声和电子注入统计扩大了阈值漫衍,从而导致器件的耐久性和数据保持特征变差。

随着人们对速率和存储容量的要求越来越高,为了提高存储密度,除了在工艺上不停缩小单元尺寸,以提高单元面积上的集成度外,更是在平面NAND 的基础上,生长了3D NAND,容量也从最初的4Mb增添到1.33Tb,实现了33.3万倍的增进。

四、 3D NAND闪存芯片的生长

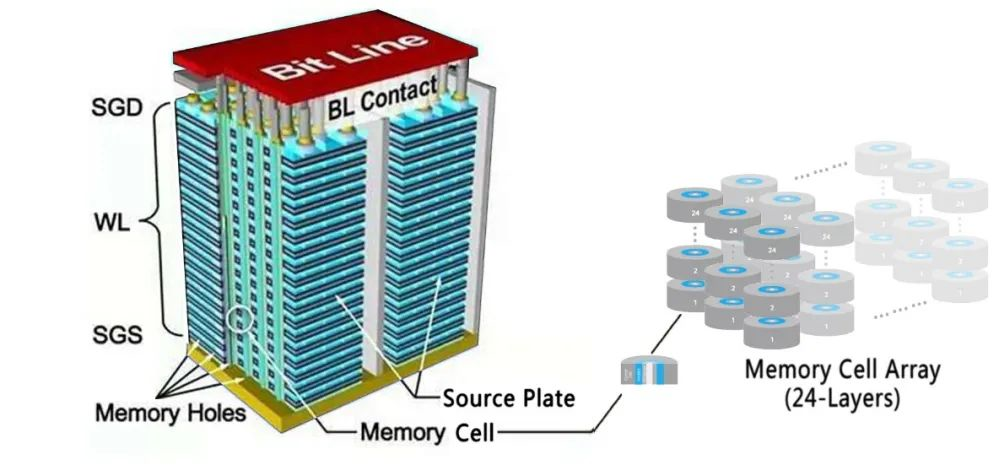

如上所述,平面NAND由具有存储单元的水平串组成。在3D NAND中,存储单元串被拉伸、折叠并以“U形”结构垂直直立。也就是说,存储单元是以垂直方式堆叠的,层数代表了堆叠在一起的字线的数目,单元密度直接随着客栈中层数的增添而增添,字线层中切割出一个垂直的柱子。当柱子与每条字线相交时,就代表了一个物理单元。这个单元就是在这个相交处形成的。

下图显示了3D NAND单元阵列架构。字符串沿垂直偏向放置。字线(WL)具有板状形状而且垂直堆叠用于3D单元堆叠。在一个块的漏极侧(SGD)有多个选择栅极。NAND串的沟道具有圆柱体形状。通过施加电压,电子被带进和带出绝缘电荷存储膜,信号被读取。

单杯30元的现制酸奶,欲做新一代“喜茶们”?

3D- NAND闪存芯片。图源:百度

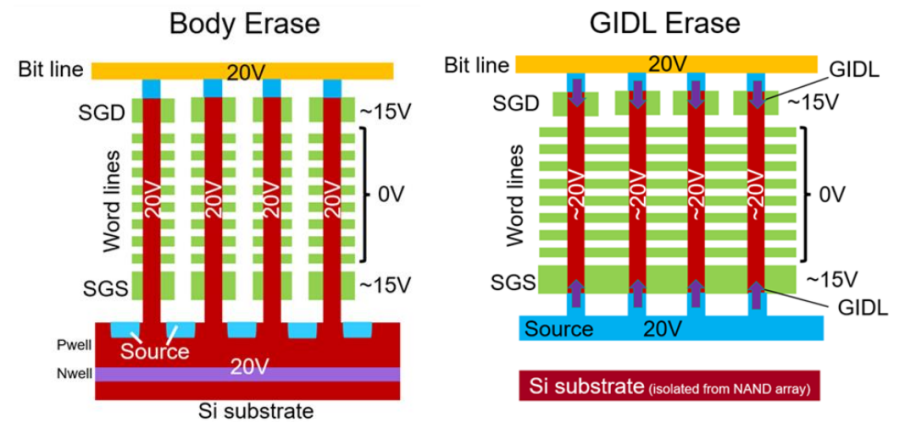

块是擦除操作的一个单元,3D NAND中有两种类型的擦除方式。划分是体擦除和GIDL擦除。体擦除中,NAND串被毗邻到Si衬底,而且空穴被从Si衬底提供应NAND串,获取正体电势,实现擦除。在GIDL擦除中,NAND串与硅衬基去耦合,形成N 源极层。在擦除时代,通过GIDL机制在源极和漏极N 结处发生电子-空穴对,以向NAND串提供空穴。

体擦除(左)和GIDL(右)擦除的原理。图源:Electronics杂志

2022年9月,基于CMOS阵列下(CuA)架构,即将 NAND 的大部门逻辑置于 NAND 存储单元之下,美国美光公司推出了全球*232层NAND。美光的232层 NAND实现了有史以来最高的每平方毫米TLC密度:14.6Gb/mm2, 比当今市场上的TLC竞品高35%到100%。232层NAND接纳新的11.5mmx13.5mm封装发货,其封装尺寸比美光前几代产物小28%。高效行使了电路板空间,更大容量和更小封装的连系更适用于种种应用场景。现在,美光的232层NAND已在该公司的新加坡工厂量产。从产物化的角度来看,这意味着美光现在还可以通过堆叠 16 个 232层 裸片来生产 2TB 存储芯片。

五、 3D NAND闪存芯片制造手艺的挑战

若何开发出尺寸更小、速率更快、功耗更少、成本更低,同时容量更大的3D NAND,一直是存储芯片制造工程师不停面临的庞大挑战。增添堆叠层数*的难题是确保堆叠从上而下的统一性,这对于准确对齐所有的层和毗邻柱是必不能少的,详细来说:

1)高纵横比(HAR)刻蚀工艺,以实现细小的垂直沟道。

2)在存储单元之间获得足够的驱动电流。

3)CMOS阵列下逻辑芯片设计优化。

4)晶圆翘曲。

3D NAND的架构有两种,一种架构是韩国三星公司提出的单层模式,例如,三星的92层3D NAND装备将所有92层堆叠在统一芯片上。三星的128层手艺在统一芯片上堆叠128层。通过将所有所需的层堆叠在一个芯片上,制造商可以削减成本和开发时间。但128层已经是单层架构的极限了。缘故原由是HAR蚀刻工艺步骤。一次蚀刻128层的堆叠现在是可行的,再多就不行了。

另一种架构是双层模式。例如,在96层器件中,一些器件将两个48层结构堆叠在相互之上。Micron将两个116层的结构堆叠在一起,从而形成232层的器件。显然,双层模式减轻了刻蚀工艺的指标要求,但增添了更多的步骤和成本。

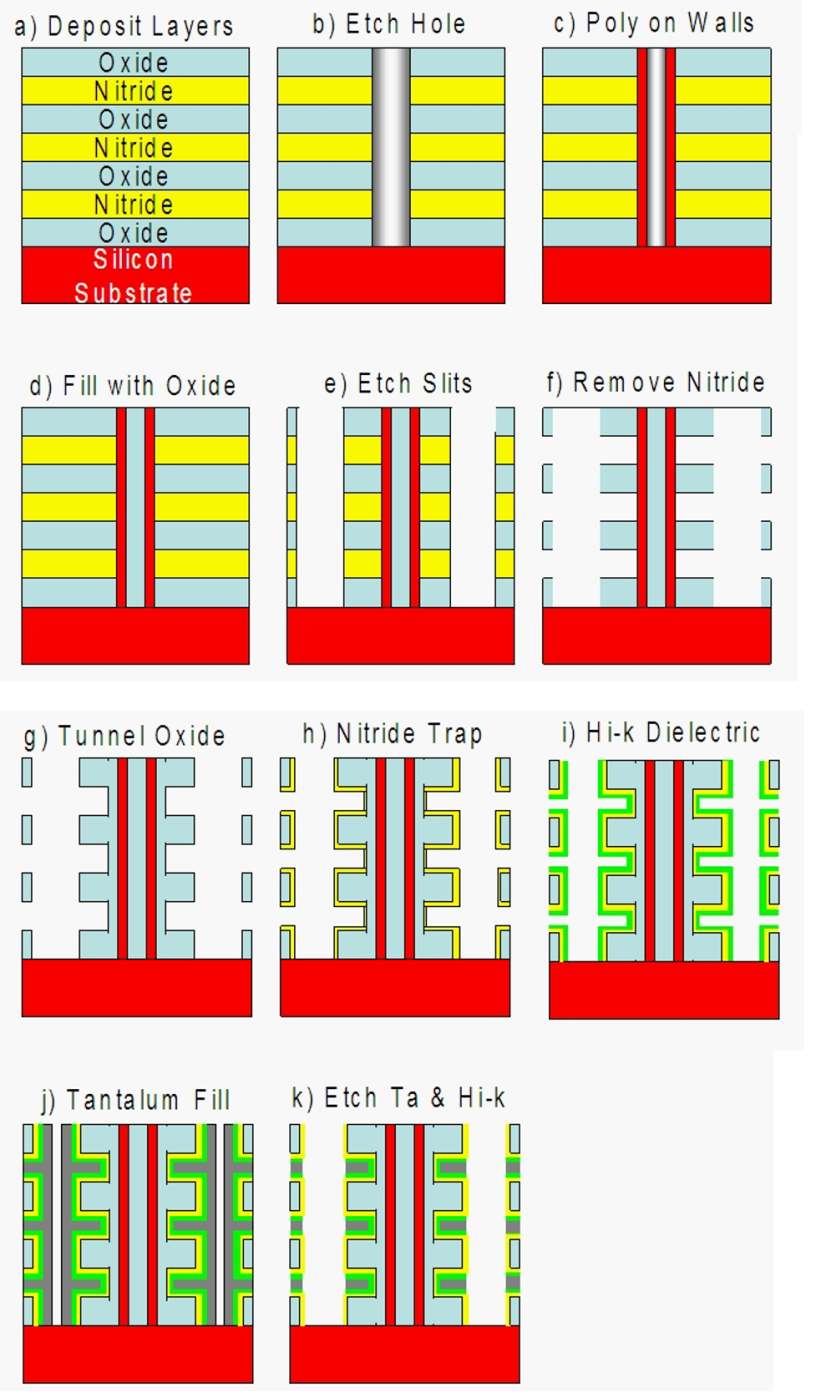

3D NAND闪存芯片制造流程。图源:Jim Handy, The Memory Guy

首先,在基底上沉积一层质料,然后在顶部沉积另一层质料。该历程重复数次,直到给定的器件具有所需的层数。每个供应商都使用差其余一组质料来确立一堆层。例如,在三星的3D NAND手艺中,该公司在基板上沉积氮化硅和二氧化硅的交替层。

理论上,供应商可以堆叠无限数目的层。但随着更多层的添加,难点在于堆叠具有正确厚度和优越平均性的层。此外,当沉积越来越多的层时,薄膜中的应力会蕴蓄起来,这可能会使晶片翘曲并扭曲图案。后续接纳双层模式时,瞄准会变得加倍难题。

HAR刻蚀是最难题的环节。刻蚀机必须从器件堆叠的顶部钻到底部衬底的细小圆孔或通道。通道使单元能够在垂直堆叠中相互毗邻。在这个历程中,首先将碳基质料沉积在叠层上。这种质料酿成了一个坚硬的遮掩层。下一步是在硬掩模的顶部形成孔的图案。刻蚀机以70:1的纵横比在统一个芯片中刻蚀出数百万个细小的通道,每个通道必须平行且平均。而且随着蚀刻工艺深入沟道,蚀刻速率趋于降低。孔也可能泛起特征尺寸的转变。

使用种种检测工具丈量单通道内部的平均性和轮廓也是难题的环节。更高的纵横比结构将带来新的、更厚的硬掩模和更宽的间距字线,进一步挑战传统的检测能力。更高的纵横比沟道孔和字线隔离进一步削弱了划线靶和器件结构之间的相关性。这些应用的计量需要转移到管芯内、器件上,并与更高的长宽比结构相一致。另外,用多晶硅质料对细小的垂直沟道举行内衬,然后用氧化物填充沟道,也是一个难点。随着垂直通道变得越来越高,层越来越多,存在沟道移动性。多晶硅沟道的迁徙率和可变性在很洪水平上取决于晶粒尺寸和陷阱密度。

六、中国NAND闪存芯片的顽强崛起

果然资料显示,2016年7月,国家存储器基地项目在武汉启动,该项目一期和二期投资达240亿美元。

果然资料显示,2016年12月22日,清华紫光团结其他公司配合出资确立长江存储科技控股有限责任公司(长江控股),实现对长江存储科技有限责任公司的控制,紫光将出资197亿元持有长江控股51.04%股权。

长江存储科技有限责任公司,即国家存储器基地,是一家专注于3D NAND闪存设计制造一体化的IDM集成电路企业,同时也提供3D NAND闪存晶圆及颗粒,嵌入式存储芯片以及消费级、企业级固态硬盘等产物息争决方案。

2017年10月,长江存储通过自主研发和国际相助相连系的方式,乐成设计制造了中国*3D NAND闪存。打破外洋半导体厂三星、SK海力士、美光、英特尔、东芝、西部数据等的手艺垄断。

2019年9月,搭载长江存储自主创新 Xtacking® 架构的第二代TLC 3D NAND闪存正式量产。与其它厂商手艺差异,长江存储首创的Xtacking®架构在两颗差其余晶圆上制造两种电路,然后再举行封装毗邻。就像搭积木一样,读写单元和存储单元可以自力生产,不仅降低生产成本,还大大提升了闪存性能。

2020年4月,长江存储宣布第三代TLC/QLC两款产物研发乐成,其中X2-6070型号作为*第三代QLC闪存,拥有公布之时业界最高的I/O速率,最高的存储密度和最高的单颗容量。

2022年8月份,长江存储正式公布200层 3D NAND闪存芯片产物X3-9070,这是基于晶栈3.0(Xtacking 3.0)架构的第四代3D TLC NAND闪存芯片。长江存储首创的Xtacking 3.0相比上一代产物,X3-9070性能提升50%,功耗降低25%。另外,该架构可以实现高效的产物开发效率,和同类厂商相比约莫能削减3个月的开发时间。X3-9070是中国有史以来存储密度最高的闪存颗粒,2022年12月最先举行量产。

需要指出的是,层数是闪存的性能最要害手艺指标,层数越多,单元空间存储密度就越大,总存储容量越容易提升。固然,接口速率、可靠性、随机读取性能、能耗、每单元位数等指标也很主要。

3D NAND闪存芯片的立体结构更依赖于刻蚀机和物理沉积装备,而不是光刻机来实现。固然,水浸没式DUV光刻机是量产高性能3D NAND闪存芯片的需要条件。然则,3D NAND闪存芯片的量产并不需要EUV光刻机。祝福长江存储的200层 3D NAND闪存芯片产物X3-9070!