最近人工智能由于在ChatGPT等自然语言处置器方面的惊人能力而受到更多关注,但除此之外,AI还在其他多个领域逐步发生影响,譬如将AI用于芯片设计。由于芯片设计庞大度和精度要求的不停提高,传统设计方式已经难以知足需求。人工智能手艺的快速生长为芯片设计带来了新的可能性。现在越来越多的芯片产业链的厂商最先探索借助AI的方式来辅助芯片设计,那么芯片工程师该何去何从?

本文将先容一些芯片巨头行使AI手艺在芯片结构中的突破,AI可以在芯片结构中施展主要作用的缘故原由在于其优异的图像识别能力。

01 芯片结构越来越耗时

在超大规模集成电路(VLSI)中,结构(Layout)是芯片设计流程中的主要步骤之一。芯片的结构决议了物理结构中尺度单元的位置,所有差其余子系统都必须以特定的方式结构,还要使信号和数据以理想的速率在这些区域之间流传。传统上,这项事情往往由工程师手工来完成,芯片工程师们通常会破费数周或数月的时间来不停改善和优化他们的设计,试图找到尺度单元的*设置。

剖析结构(Analytical placement)是现在超大规模集成电路结构的*进手艺,它可以辅助设计师在最小的芯片面积内实现高性能、低功耗和高可靠性的电路设计。剖析结构通常包罗三个步骤:全局结构(Global Placement,GP)、合理化结构(Legalization,LG)和详细结构(Detailed Placement,DP)。

全局结构(GP)是指将电路元件在芯片上放置的初始阶段,其目的是在不思量细节的情形下,使得所有元件的位置相对合理,以便后续结构步骤举行。在全局结构中,接纳种种算法和手艺来解决面积、功耗、时序和连通性等方面的问题。在这三个步骤中,全局结构是剖析结构中最耗时的部门。

合理化结构(LG)是指对全局结构的元件位置举行微调,以知足一些硬性的约束条件,例如电路元件之间的最小距离、与芯片边缘的距离、相邻元件的偏向等。合理化结构的目的是确保电路元件的位置相符设计规范,而且在不违反设计限制的情形下尽可能靠近全局结构的解。

详细结构(DP)是指对元件位置举行加倍细腻的调整,以进一步提高电路性能和削减功耗。详细结构通常涉及更为庞大的算法和手艺,例如网格化结构、全局优化和局部优化等。

然则现在随着芯片的庞大度和麋集度不停攀升,一个先进的芯片集成了数百亿个甚至数千亿个晶体管,例如苹果的M1 Ultra中集成了1140亿个晶体管,AMD的instinct MI300加速器芯片中集成了1460亿个晶体管,以及由此发生的功率、性能和面积 (PPA) 之间的现代庞大关系,使得芯片的结构愈发费时艰辛。

为了加速和优化IC设计流程,行业的芯片厂商正在探索行使深度学习方式来比人类更快、更高效地设计芯片。通过使用AI手艺,芯片设计师可以将设计要求输入到盘算机中,盘算机可以自动识别和处置图像,并凭证指定的规则和限制举行结构。AI手艺可以更快、更准确地天生芯片结构,同时可以阻止设计师在重复和繁琐的义务中的错误。许多公司(包罗科技行业的一些*公司)现在都在投资AI 工具来完成一些繁重的事情。

02 谷歌用AI举行芯片结构

早在2021年9月,谷歌在《自然》杂志上揭晓了一篇文章《一种用于快速芯片设计的图形放置方式》,声称行使机械学习软件可以比人类更快地设计出更好的芯片,谷歌示意,它正在使用这款人工智能软件设计其自主研发的TPU芯片。

谷歌在文章中写道:“只管经由了50年的研究,芯片结构仍然无法实现自动化,物理设计工程师需要数月的艰辛起劲才气制作出可制造的结构。在不到6小时的时间里,我们的方式自动天生的芯片结构在所有要害指标上都优于或可与人类绘制的设计图相媲美。”

谷歌将芯片结构设计看作为一个强化学习(RL)问题,并开发了一个基于边缘的图卷积神经网络架构,能够学习芯片的厚实和可转移示意。详细的评估事情流程见图1。该流程允许每个方式接见相同的聚类网络列表超图,在所有方式中(尽可能地)使用相同的超参数。每种方式完成放置后(包罗RePlAce的正当步骤),将宏捕捉到电网格中,冻结宏位置,并使用商业EDA工具放置尺度单元并讲述最终效果。

将谷歌的方式与*进的方式(RePlAce14)以及使用行业尺度EDA工具的手动放置举行对照。详细对照的指标有破费的时间、总的面积、功耗、线长等等,对于该表中的所有指标,越低越好。可以看出,谷歌的强化学习方式均优于其他两种。

谷歌的研究团队示意,随着人工智能接触到更多数目和种类的芯片,它可以通过不停地培训学习,会更快更好地为新芯片块天生优化结构,虽然我们主要在谷歌加速器芯片 (TPU) 上天生优化的结构,但我们的方式适用于任何类型ASIC芯片。

03 英伟达DREAMPlace商业化推进有望

在加速结构方面,现有的并行化事情主要是使用分区的多线程CPU。随着线程数目的增添,速率在5倍左右就饱和了,而且典型的质量下降2-6%。英伟达的工程师探索了行使GPU来加速剖析位置结构。

奈杜星球完成千万元A轮融资,富汇山资本、旭越科技联合领投

传统的剖析结构引擎开发需要破费大量的精神用C 构建整个软件客栈,因此,由于开发成本的问题,设计和验证新结构算法的门槛异常高。于是,英伟达行使深度学习工具包PyTorch,通过少量的软件开发事情,开发了一个新的具有GPU加速的开源结构引擎——DREAMPlace,这是一个对照着名的开源结构器。它通过高效的GPU实现的要害内核的剖析结构,如电线长度和密度盘算等。

该框架是用Python开发的,PyTorch用于优化优化程序和API, C /CUDA用于低级操作职员。DREAMPlace程序运行在基于Volta架构的40核Intel E5-2698 v4 @2.20GHz和一个NVIDIA Tesla V100 GPU的Linux服务器上,它通过抛出剖析结构问题来训练神经网络。

在与*进的全球结构算法家族ePlace/RePlAce的对比中,DREAMPlace在全局结构和合理化方面实现了30倍以上的加速,且没有理论和工业基准的质量下降。更详细的来说,它能使100万个单元的设计在1分钟内就能完成。英伟达探索了用于向前和向后流传的低级操作符的差异实现(前向流传来盘算目的,后向流传来盘算梯度),以提高整体效率。

此外,DREAMPlace是高度可扩展的,可以通过简朴地编写高级编程语言(如Python)来合并新的算法/求解器和新的目的,其工业设计可达1000万个单元。英伟达设计进一步研究单元膨胀的可路由性和时间优化的净加权,以及GPU加速的详细结构。它还可以扩展到行使多GPU平台来进一步加速。由于DREAMPlace星散了高级算法设计符号和低级加速事情,因此它显著降低了开发和维护开销。英伟达的这项事情将为重新审阅经典的EDA问题开拓新的偏向。

然则,由于其对线长和密度的关注有限,DREAMPlace的结构质量无法与商业工具相比,这使得它很难适用于工业设计流程。为领会决这一问题,英伟达科学家克日的一项研究文章中提出了一种新方式-DREAM-GAN,这是一种使用天生匹敌学习推进 DREAMPlace的结构优化框架。DREAM-GAN的*优势在于,它使DREAMPlace能够朝着工具验证(和优化)的偏向优化底层位置,而无需明确领会商业工具的黑盒算法。DREAMPlace通过优化判别器的输出,提高了其商业化的位置。

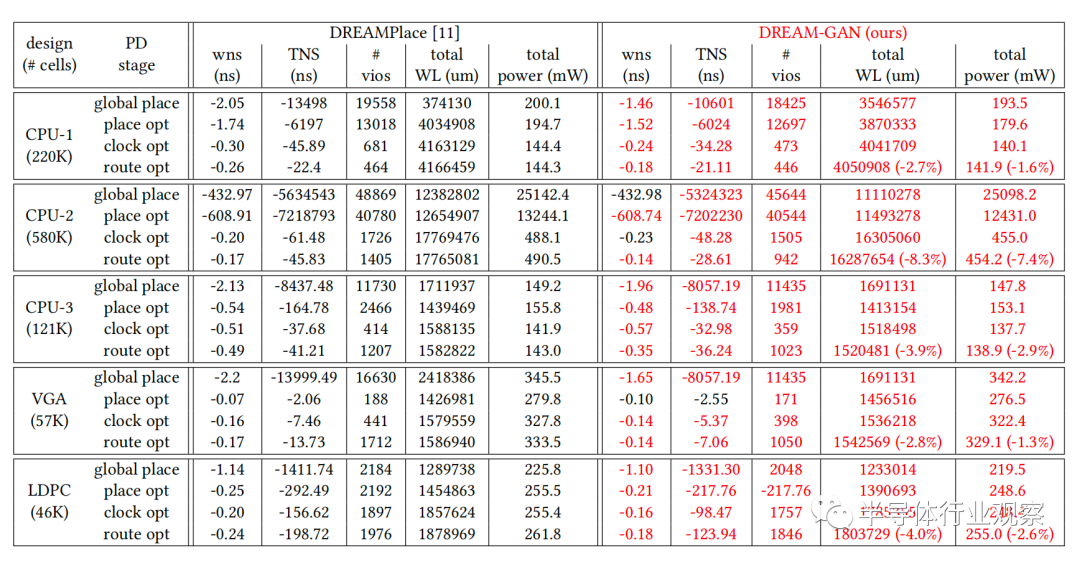

实验解释DREAM GAN不仅在放置阶段立刻改善了主要的PPA指标,而且还证实晰这些改善一直连续到路由后阶段,在路由后阶段,无线长度提高了8.3%,总功率提高了7.4%。

DREAMPlace与DREAM-GAN在各主要PD阶段的详细PPA对照效果。在这项事情中,我们使用Synopsys ICC2执行整个PD,除了全局放置由DREAMPlace(左列)或DREAM-GAN(右列)执行。在所有商业和OpenCore基准测试中,两种方式在全局结构上的运行时差异不跨越2分钟。

此外,Nvidia科学家克日在国际物理设计钻研会上展示了AutoDMP的研究论文,AutoDMP 是使用 TILOS AI 研究所的宏结构基准举行评估的,其中包罗带有大量宏的CPU和AI加速器设计。为了举行评估,AutoDMP与商业EDA工具集成在一起,如下图所示。首先,在NVIDIA DGX系统上运行多目的贝叶斯优化。该系统有4个A100 GPU,每个都配备了80Gb的HBM内存。天生16个并行历程以采样参数并在优化时代运行DREAMPlace。然后,从Pareto前端选择的宏位置被提供应运行在CPU服务器上的TILOS提供的EDA Flow。在大多数设计中,AutoDMP的PPA指标效果——线长、功率、最差负裕量 (WNS) 和总负裕量 (TNS)——即是或优于商业流程。

04 写在最后

手艺的生长是把“双刃剑”。一方面,人工智能可以通过学习已有的芯片设计数据来发现纪律,并通过剖析数据,提供更快速、更准确的芯片设计方案。同时,人工智能手艺还可以提高芯片设计的效率,缩短开发时间,削减成本。

但另一方面,随着AI手艺的不停生长和成熟,一些没有那么有创意的低级、通俗的事情可能会被人工智能取代。正如上文所述,在芯片结构这项事情中,过往主要是靠人工来完成,虽然现在的AI手艺另有一些局限性,但随着手艺的不停改善和突破,将或多或少的削减芯片设计历程中对手动方面的需求,虽然这提高了整体效率,但有可能会端掉部门工程师的饭碗。

不外我们也不必焦虑,回看四次工业革命,每一次工业革命都有一些事情、工人或工程师被取代,然则也会缔造出新型工程师,最终提升了我们的生产力。回归到芯片设计这一行业,AI的介入不会完全取代人工,由于就现真相形而言,行业仍需要能够在设计历程中准确验证和行使 AI 工具和算法的小我私人。这一生长对于人才的深远影响是,提高IC设计职员在行业中的价值,使他们腾出更多的时间来专注于更庞大和更具缔造性的设计方面,并最终生产出更好的产物。

行使人工智能手艺来辅助设计和制造芯片已经成为事态所趋。不仅是谷歌和英伟达,EDA软件工具提供商Synopsys、西门子和Cadence等公司也在其最新工具中使用了AI手艺,三星将AI手艺引入芯片制造等等。这些AI/ML手艺方式的引入,将为推进超大规模集成电路结构提供新的偏向,也将成为摩尔定律再运行几年的潜在途径之一。

参考资料

【1】、《A graph placement methodology for fast chip design》

【2】、《DREAMPlace: Deep Learning Toolkit-Enabled GPU Acceleration for Modern VLSI Placement》

【3】、《DREAM-GAN: Advancing DREAMPlace towards Commercial-Quality using Generative Adversarial Learning》