在高性能盘算系统,稀奇是AI服务器中,内存(DRAM)的容量和带宽指标越来越主要,由于处置器需要处置巨量数据,传统DRAM已经无法知足需求。现在,HBM是当红炸子鸡。

相对于传统DRAM,HBM的制造要庞大许多,它需要将多个DRAM裸片堆叠在一起,这就需要用到较为先进的封装手艺了。

随着手艺提高和市场需求的转变,HBM客栈的密度也在增添,有机构统计,根据当下的势头生长下去,将从2022年的16GB增添到2027年的48GB,DRAM大厂美光加倍乐观,预计2026年将泛起64GB的HBMNext(HBM4),堆叠层数能到达16,这样,使用16个32Gb的DRAM裸片就可以构建64GB的HBM模块,这需要存储器制造商进一步缩小DRAM裸片的间距,需要用到新的生产手艺,稀奇是更好的封装手艺。

通常情形下,HBM客栈使用硅通孔(TSV)垂直毗邻多个DRAM裸片,这种带有TSV的堆叠架构允许异常宽的内存接口(1024位)、高达36GB、64GB的内存容量,并可实现跨越1TB/s的带宽。

生产HBM堆叠芯片比生产传统的DRAM要庞大得多。首先,用于HBM的DRAM裸片与典型DRAM(例如DDR4、DDR5)完全差异,内存生产商必须制造出足量的DRAM裸片,并对它们举行测试,然后将它们封装在预先测试好的高速逻辑芯片层之上,最后测试整个封装。这个历程既昂贵又耗时。

以最新量产的HBM3E为例,其芯片尺寸约莫是一致容量DDR5的两倍,除了逻辑层和DRAM层,还需要一个接口层,云云庞大的封装客栈,会影响良率。因此,随着HBM的生长,堆叠层数不停增多,封装庞大度也在增添,其制造难度越来越大,且良率难以提升。

01 3D DRAM接力

HBM并不是高性能盘算系统用内存的最终形态,从各大存储器厂商的研发偏向来看,在存算一体彻底解决“存储墙”问题、相关芯片手艺成熟并实现量产之前,3D DRAM将是HBM的继任者。

传统DRAM需要庞大的读写数据操作流程,而3D DRAM可以通过垂直堆叠的存储单元直接存取和写入数据,显著提高了存取速率。3D DRAM的优势不仅包罗高容量和快速数据接见,还具有低功耗和高可靠性特点,可以知足种种应用需求。

这里先简朴先容一下DRAM的基本结构。

DRAM单元电路由一个晶体管和一个电容器组成,晶体管认真传输电流,使信息(位)能够被写入或读取,电容器则用于存储位。

DRAM由被称为“位线(BL)”的导电质料组成,位线提供注入晶体管的载流子(电流)。晶体管就像一个闸门,可以打开(接通)或关闭(断开),以保持或住手电流在器件内的流动。这种栅极状态由施加在被称为“字线(WL)”的接触导电结构上的电压偏置来界说,若是晶体管导通,电流将流过晶体管到达电容器,并存储在电容器中。

电容器需要有较高的深宽比,这意味着它的高度远大于宽度。在一些早期的DRAM中,电容器的有源区被嵌入到硅衬底中,在最近几代DRAM中,电容器则是在晶体管顶部举行加工。

3D DRAM是将DRAM单元垂直堆叠,是一种具有全新结构的存储芯片,打破了原有的模式,它有些类似已经成熟的3D NAND单元垂直堆叠,但制造难度比3D NAND大。3D DRAM不是简朴地将2D DRAM组件堆叠在一起,也差异于HBM,需要重新设计DRAM架构,需要用到一些先进的晶体管制造手艺和先进封装手艺。

3D DRAM设计重点是解决制程节点微缩和多层堆叠的难题,另外,另有电容器和晶体管微缩,以及单元间毗邻和通孔阵列,还要制订响应的工艺规格。通过垂直堆叠,3D DRAM芯片将单元面积的容量增添3倍。3D DRAM与HBM在设计和制造层面都是纷歧样的。

据The Elec报道,三星和SK海力士都已将夹杂键合确定为未来制造3D DRAM的要害封装手艺。据悉,三星设计在2025年推出3D DRAM芯片,SK海力士还没有确定详细时间。现在,三星和SK海力士使用微凸块来毗邻DRAM模块,夹杂键合手艺可以通过使用硅通孔垂直堆叠芯片,以消除对微凸块的需求,从而显著削减芯片厚度。

02 制造3D DRAM,要解决几个问题

为了推进DRAM制程微缩,需要将2D DRAM组件侧放并堆叠起来,但这会晤临一些难题:水平偏向需要横向刻蚀,但由于凹槽尺寸差异很大,横向刻蚀异常难题;在客栈刻蚀和填充工艺中需要使用差其余质料,这给制造带来了难题;毗邻差异3D组件时存在集成难题。

在制造3D DRAM时,需要缩短电容器(Cap)的长度(电容器的长度不能和高度一样),并举行堆叠,以提升单元面积的存储单元数目。

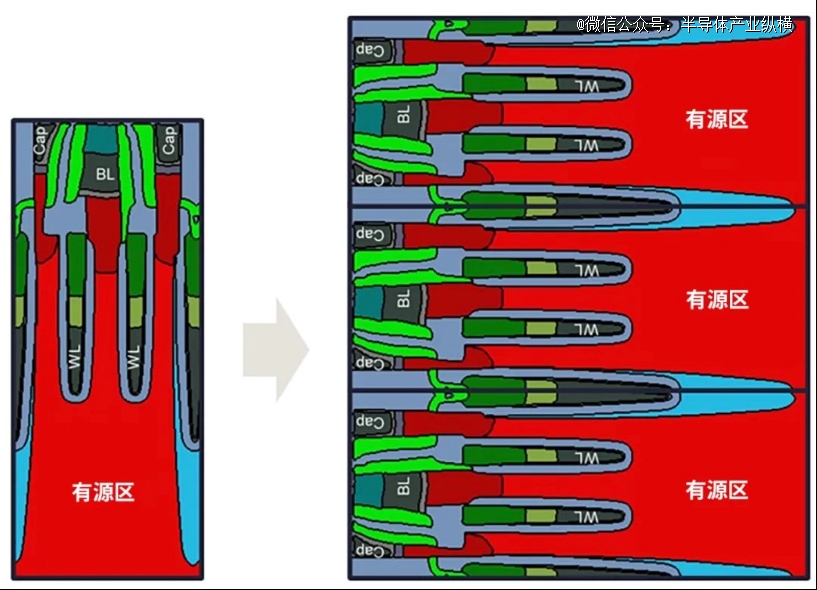

图:2D DRAM架构垂直定向视图(左图),将其翻转并将结构堆叠在一起(右图)的做法不能行的主要缘故原由是需要刻蚀横向空腔,并将其以差其余横向深度填充到硅有源区中。

图:2D DRAM架构垂直定向视图(左图),将其翻转并将结构堆叠在一起(右图)的做法不能行的主要缘故原由是需要刻蚀横向空腔,并将其以差其余横向深度填充到硅有源区中。

上图示意的结构稳固,将其顺时针旋转90度,结构将处于自上而下的视图中。在这个偏向上,可以堆叠纳米薄片。然则,这种情形下,原始设计显示的区域异常麋集,因此,位线和电容器需要自上而下地举行工艺处置,而且距离很近。要实现这种偏向的3D堆叠,需要重新设计架构。

除了要设计新架构,还必须改变3D DRAM的金属化和毗邻性,需要设计新方式来促使电流通过中央的位线堆叠,包罗毗邻各层的水平MIM(金属-绝缘层-金属)电容器阵列,以及将栅极包裹在晶体管周围(栅极全笼罩)。其原理是,当电流通过时,只有目的位线(层)被激活,在被激活的层中,电流可以毗邻到准确的晶体管。

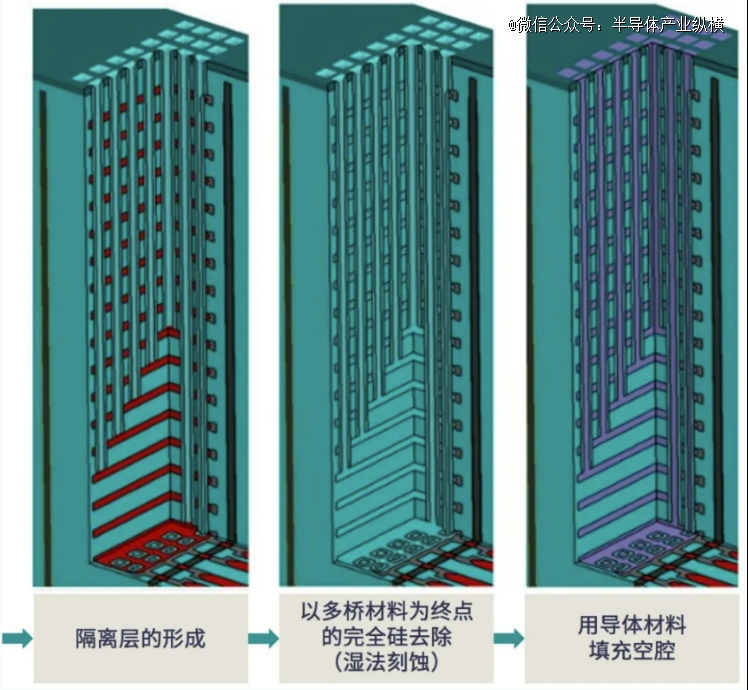

另有硅通孔阵列问题。为了阻止3D NAND中使用的台阶式结构的局限性,需要引入穿过硅客栈层且可以在特定层住手(每层一个通孔)的通孔阵列结构,将接触点置于存储单元内部。沟槽制作完成后,可以引入只存在于侧墙的隔离层。

高沟槽用于引入刻蚀介质以去除硅,然后在空沟槽中引入导电金属。其效果是,顶部的每个方格(下面最后三张图片中的浅绿色和紫色方框)只与下面的一层毗邻。

东方甄选最近有点「乱」

工艺方面,需要怪异且创新的工艺,3D DRAM是一种前沿设计,要想实现量产,接纳的工艺和设计是从未见过或实验过的。

03 3D封装助阵

以上先容的是3D DRAM在芯片设计和制造工艺方面的挑战息争决思绪,响应的裸片制造出来后,需要更适合、更先进的封装手艺,将这些DRAM裸片和逻辑等功效部门有机地连系在一起,才气使应用效能*化。

越需要用到先进封装的地方,说明被封装的裸片越小,封装在一起的整体庞大度越高,3D DRAM则充实涵盖了这两点。先进封装包罗2.5D和3D封装,2.5D 难以知足3D DRAM封装要求,必须接纳垂直堆叠超小型构建块(DRAM裸片),并通过硅通孔实现互连的3D封装。

在2.5D封装中,逻辑单元、内存或其它类型的芯片使用倒装芯片方式水平堆叠在硅中介层上,用微凸块毗邻差异芯片的电子信号,通过中介层中的硅通孔毗邻到下面的金属凸块,然后封装到IC基板上,在芯片和基板之间确立更慎密的互连。从侧面看,虽然芯片是堆叠的,但本质仍然是水平封装(传统芯片封装都是水平的)。不外,与传统封装相比,2.5D封装中的裸片巨细和间距小了许多,靠近3D封装。

3D封装要将多个裸片(面朝下)堆叠在一起,直接使用硅通孔垂直堆叠,将上方和下方差异裸片的电子信号毗邻起来,实现真正的垂直封装。现在,越来越多的 CPU、GPU和内存最先接纳3D封装手艺。

到了3D封装阶段,夹杂键合手艺险些是必选项。

夹杂键合是芯片封装工艺中使用的芯片键合手艺之一,常用的商用手艺是“Cu-Cu夹杂键合”。使用Cu-Cu夹杂键合,金属触点嵌入到介电质料中,通过热处置工艺,这两种质料连系在一起,行使固态铜金属的原子扩散来实现键合。这种方式解决了以前倒装芯片键合工艺中遇到的挑战。

夹杂键合不是*的先进封装手艺,但它提供了最高密度的垂直堆叠。封装中的微凸起占用的体积使得客栈太高,无法放入带有GPU或CPU的封装中,夹杂键合不仅会缩小DRAM裸片的高度,还可以更容易地从封装中去除多余的热量,由于这种封装各层之间的热阻较小。

与倒装芯片键合相比,夹杂键合具有多种优势,它允许实现超高的I/O数目和更长的互连长度,通过使用介电质料取代底部填料举行粘接,消除了填充成本。此外,与晶圆上的芯片键合相比,夹杂键合的厚度最小,这对于需要堆叠多层芯片的3D DRAM封装稀奇友好,由于夹杂键合可以显著降低整体厚度。

04 三大厂商的3D DRAM制造希望

现在,三星、SK海力士和美光这三大存储芯片厂商都在研发3D DRAM,响应的制造工艺和封装手艺也在同步开发中。

美光从2019年起就最先了3D DRAM的研究,拥有30多项与3D DRAM相关的专利,获得的专利数目是三星和SK海力士的2~3倍。

近些年,三星一直在举行3D DRAM的研究,并推出了业界*12层3D-TSV手艺。

2023年,在日本举行的“VLSI钻研会”上,三星电子揭晓了一篇包罗3D DRAM研究功效的论文,并展示了3D DRAM芯片内部结构的图像。

据新闻人士称,2023年5月,三星电子在其半导体研究中央内组建了一个开发团队,大规模生产4F2结构DRAM。由于DRAM单元尺寸已到达极限,三星想将4F2应用于10nm级工艺或更先进制程的DRAM。若是三星的4F2 DRAM存储单元结构研究乐成,在不改变制程的情形下,裸片面积可比现有6F2 DRAM存储单元削减约30%。

据悉,三星已经将3D DRAM堆叠至16层。

SK海力士正在为未来的DRAM开发IGZO通道质料,它可以改善DRAM的刷新特征。据悉,IGZO薄膜晶体管依附其适中的载流子迁徙率、极低的泄电流以及基板尺寸的可扩展性,在显示面板行业耐久获得应用。它可以成为未来 DRAM 可堆叠通道质料的候选方案。

最近,在夏威夷举行的VLSI 2024峰会上,SK海力士宣布了3D DRAM的最新研究功效,其5层堆叠的3D DRAM良率已达56.1%。此外,SK海力士的实验性3D DRAM在性能上已展现出与2D DRAM相媲美的特征,然则,在实现商业化之前,仍需举行大量的手艺验证和优化事情。

05 结语

作为芯片行业的大宗商品,DRAM原本就具有重大的市场份额,现在,在高性能盘算需求的推动下,种种新的内存手艺和产物依次泛起,给这一原本就很热闹的市场增添了更多看点。

随着AI服务器的生长,HBM迅速走红,相关芯片的制造和封装是当下产业的热门话题。随着应用的生长和手艺水平的提升,未来几年,3D DRAM很可能会替换当下HBM的行业职位,因此,相关芯片制造和半导体装备厂商都在研发上投入越辣越多的资源,不停蓄力。

就芯片制造和封装而言,3D DRAM还需要继续攻关,距离量产另有一段时间。对此,SK海力士指出,虽然3D DRAM有着伟大的生长潜力,但在实现商业化之前仍然需要做大量事情。现在,3D DRAM显示出的性能特征依然很不稳固,需要到达32~192层堆叠的存储单元才气普遍使用。